拆开一颗 FPGA:内部资源完全图鉴

💡 在前几篇文章中,我们知道了 FPGA 是”一块可以反复编程的数字逻辑芯片”,也了解了它的发展历程和市场格局。但有一个关键问题还没回答:

FPGA 内部到底长什么样?你写的 Verilog 代码,最终会变成芯片里的什么东西?

这篇文章会带你”拆开”一颗 FPGA,逐一认识它的内部资源。读完之后,你再看 Vivado 的综合报告里那些 LUT、FF、BRAM、DSP 的数字时,就不再是一头雾水了——你会知道它们是什么、在哪里、怎么工作。

目录

- 1. 全局视角:FPGA 的内部地图

- 2. CLB:FPGA 的逻辑心脏

- 3. IOB:与外部世界的接口

- 4. 可编程互联:芯片内部的高速公路网

- 5. 专用硬核资源:内置的加速器

- 6. 全局网络:时钟与控制信号的高速通道

- 7. 总结

- 常见问题

- 参考资料

1. 全局视角:FPGA 的内部地图

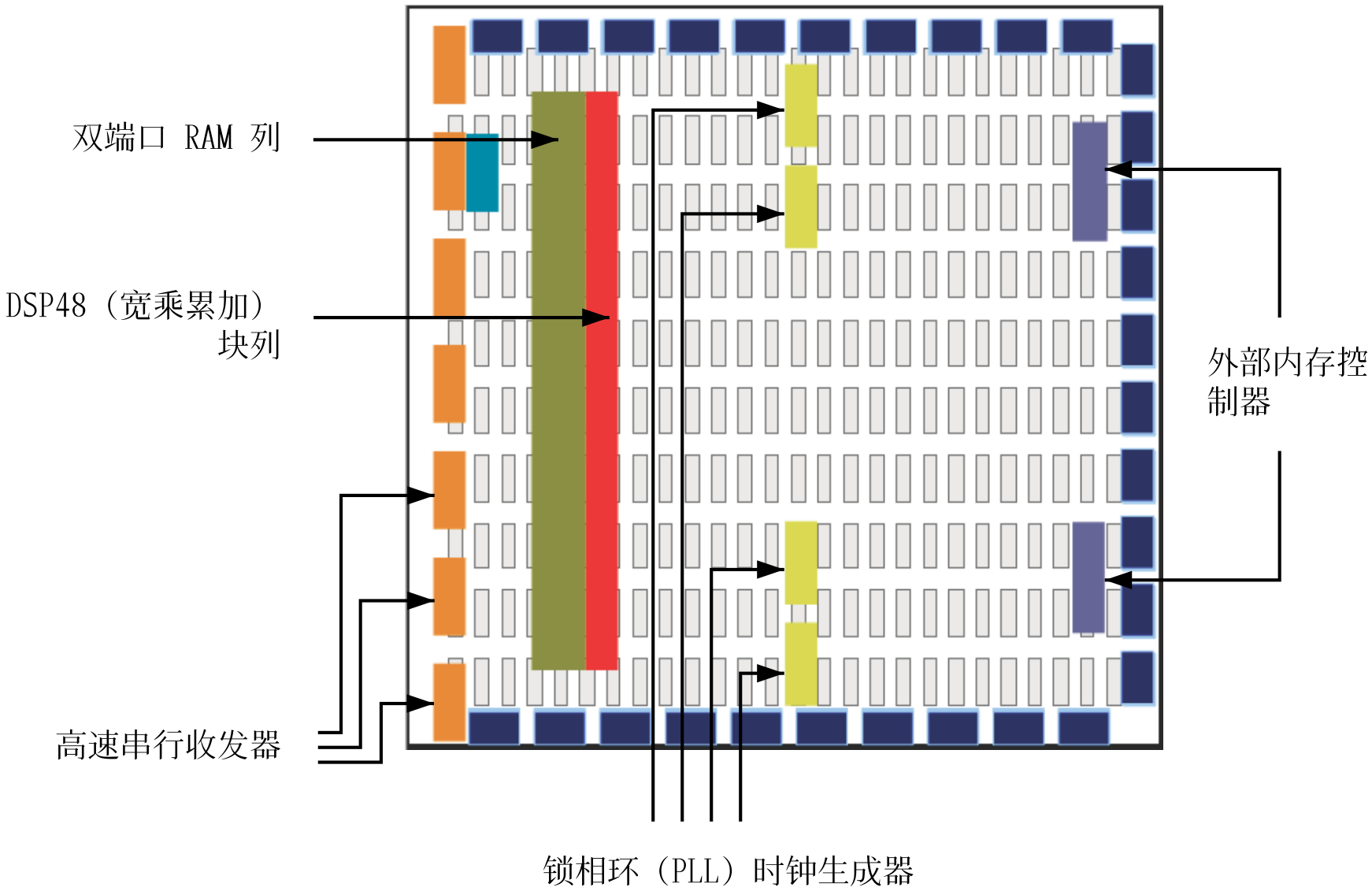

打开一颗 FPGA 芯片(以 Xilinx 7 系列为例),你会看到这样的布局:

FPGA 内部的资源可以分为六大类:

| 资源类型 | 名称 | 一句话作用 |

|---|---|---|

| 逻辑资源 | CLB(可配置逻辑块) | 实现你写的所有逻辑——组合逻辑、时序逻辑、状态机 |

| I/O 资源 | IOB(输入输出块) | FPGA 与外部芯片/传感器/接口的信号桥梁 |

| 互联资源 | Programmable Interconnect | 把所有资源连接起来的”高速公路网” |

| 存储资源 | Block RAM(块存储器) | 片上高速存储,用于缓存、FIFO、查找表 |

| 运算资源 | DSP Slice(数字信号处理单元) | 硬核乘法器+累加器,专为乘加运算优化 |

| 时钟资源 | PLL / MMCM / 全局时钟网络 | 时钟的倍频、分频、移相和全芯片分发 |

Xilinx 最新系列采用 ASMBL(Advanced Silicon Modular Block)架构——每类资源以”列”的形式排布,不同系列通过增减列数来调整资源配比。

💡 工程师手记:我第一次打开 Vivado 的 Device View,看到那密密麻麻的 CLB 阵列和穿插其中的 BRAM/DSP 列时,有一种”看到城市卫星地图”的感觉——CLB 是居民楼,BRAM 是仓库,DSP 是工厂,IOB 是城市出入口,布线资源就是纵横交错的道路。理解了这张”地图”,你对 FPGA 的认知就从抽象概念变成了具象画面。

2. CLB:FPGA 的逻辑心脏

CLB(Configurable Logic Block,可配置逻辑块) 是 FPGA 中占比最大、最核心的资源。你写的绝大多数 Verilog 代码,最终都会映射到 CLB 上。

CLB 的内部结构

一个 CLB 包含若干个 Slice(切片),每个 Slice 又包含:

| 组件 | 数量(每 Slice) | 作用 |

|---|---|---|

| LUT(查找表) | 4 个 | 实现任意 6 输入组合逻辑 |

| FF(触发器) | 8 个 | 存储数据,实现时序逻辑 |

| Carry Chain(进位链) | 1 条 | 加速加法/减法/比较运算 |

| MUX(多路选择器) | 若干 | 扩展逻辑功能和信号路由 |

不同厂商的叫法不同:Xilinx 叫 CLB/Slice,Intel(Altera)叫 LAB/ALM。但核心构成一样:LUT + 触发器 + 进位链 + MUX。

LUT:最核心的组件

LUT(Look-Up Table,查找表) 是实现组合逻辑的最基本单元。它的本质就是一个小型 RAM:

- 一个 6 输入 LUT 内部有 2⁶ = 64 个 SRAM 存储单元

- 输入信号作为地址线,选中对应存储单元中预存的值作为输出

- 配置 FPGA 时,综合工具会把你的逻辑函数的真值表写入 LUT 的 SRAM 中

举个例子——用 LUT 实现一个 3 输入与门 Y = A & B & C:

assign y = a & b & c;综合工具会把真值表写入一个 LUT:地址 111 → 存 1,其余地址 → 存 0。运行时,输入 A=1, B=1, C=1,地址 111 被选中,LUT 输出 1。

LUT 的精妙之处在于:不管你实现什么 6 输入逻辑函数,消耗的资源和延迟都完全相同——因为它不是”计算”结果,而是”查表”。

💬 你可能会问:如果我的逻辑超过 6 个输入怎么办?

综合工具会自动用多个 LUT 级联来实现。比如一个 8 输入的比较器

(a[3:0] == b[3:0])需要 8 个输入,会用 2-3 个 LUT 级联完成。级联越多,延迟越大——这就是为什么 FPGA 设计要关注”逻辑级数”。

Slice 的两种类型:SliceL vs SliceM

Xilinx 7 系列的 Slice 分为两种:

| 类型 | 功能 | 附加能力 |

|---|---|---|

| SliceL(Logic) | 标准逻辑——LUT + FF + Carry Chain | 无 |

| SliceM(Memory) | SliceL 的全部功能 + 额外能力 | LUT 可配置为分布式 RAM 或移位寄存器(SRL) |

SliceM 中的 LUT 除了做逻辑查找表,还能充当小型存储器(64×1 RAM)或高效移位寄存器(最多 32 位的 SRL32)。这个特性在数据流水线延迟、FIFO、去抖动等场景中非常实用。

FF(触发器)与 Carry Chain(进位链)

- FF(D 触发器):在时钟边沿锁存数据,是实现时序逻辑的核心。每个 Slice 有 8 个 FF,支持同步/异步的复位/置位

- Carry Chain(进位链):FPGA 内置的加法/减法专用硬件通路。当你写

c = a + b时,综合工具会自动使用进位链来加速进位传播——比纯 LUT 实现快得多

💡 工程师手记:Carry Chain 是一个”你不需要主动使用、但必须知道它存在”的资源。写

c = a + b时综合工具会自动利用它。但如果你发现加法器的时序不过关,可以考虑流水线拆分——这时候理解 Carry Chain 的工作原理就很有帮助了。

3. IOB:与外部世界的接口

IOB(I/O Block,输入输出块) 环绕在 FPGA 芯片的四周,负责信号的输入和输出。

IOB 的核心功能

| 功能 | 说明 |

|---|---|

| 电平转换 | 将外部电压(1.2V~3.3V)转为内部逻辑电平 |

| 多标准支持 | 同一引脚可配置为 LVCMOS、LVDS、HSTL、SSTL 等标准 |

| DDR 寄存器 | 支持双倍数据速率,时钟上升沿和下降沿都传数据 |

| 三态控制 | 双向引脚——同一引脚既能输入也能输出 |

| 上下拉电阻 | 可配置内部上拉/下拉,防止悬空引脚 |

Bank 组织结构(重要)

FPGA 的 IOB 按 Bank 分组管理,同一 Bank 内的所有引脚共享同一个 VCCO(I/O 电压)。

这意味着:

- 同一 Bank 内的引脚必须使用兼容的电气标准(如 Bank 的 VCCO=3.3V,则只能用 LVCMOS33)

- 差分信号的 P/N 对必须在同一 Bank 内

- 引脚分配要提前规划,否则后期改动会牵一发动全身

💬 你可能会问:什么是 HR Bank 和 HP Bank?

高端 FPGA 将 Bank 分为两类:HR(High Range)Bank 支持 1.2V

3.3V 的宽电压范围,HP(High Performance)Bank 只支持 1.2V1.8V 但性能更高。选引脚时需要注意你的接口标准与 Bank 类型是否匹配。

4. 可编程互联:芯片内部的高速公路网

CLB 是”建筑物”,IOB 是”出入口”,那可编程互联资源就是连接一切的”道路网”。

FPGA 的布线资源按用途分为四类:

| 类型 | 用途 |

|---|---|

| 全局布线 | 时钟信号和全局复位/置位的分发 |

| 长线资源 | Bank 之间的高速信号传输 |

| 短线资源 | 相邻逻辑单元之间的互联 |

| 分布式布线 | 专用的控制信号线 |

信号在芯片内部的传输需要通过两种关键组件:

- CB(连线盒):将 CLB 的输入输出接入布线通道

- SB(开关盒):在水平和垂直布线通道之间切换方向

布线资源的质量直接影响设计的时序性能。如果你的设计布线拥堵(资源利用率过高),时序就会恶化。这就是为什么 FPGA 的资源利用率建议控制在 70-80% 以内。

5. 专用硬核资源:内置的加速器

除了通用的 CLB 逻辑资源,FPGA 还内置了多种硬核 IP(Hard IP)——它们是固化在硅片上的专用电路,不占用 CLB 资源,而且性能远优于用 LUT 搭建的等效实现。

| 硬核资源 | 全称 | 作用 | 典型应用 |

|---|---|---|---|

| Block RAM | Block Random Access Memory | 片上高速存储(18Kb/36Kb 块) | FIFO、双口 RAM、ROM 查找表 |

| DSP Slice | Digital Signal Processing | 硬核乘法器+累加器(如 DSP48E1) | 滤波器、FFT、矩阵运算 |

| PLL/MMCM | Phase-Locked Loop | 时钟倍频、分频、移相 | 生成各种频率的时钟 |

| SerDes | Serializer/Deserializer | Gbps 级高速串行收发 | PCIe、以太网、HDMI |

| PCIe 硬核 | PCIe Controller | PCIe 协议控制器 | 主机通信接口 |

| Memory Controller | DDR Controller | DDR 存储器接口控制 | 外部 DDR3/DDR4 存储 |

Block RAM 使用示例:

// 用 Block RAM 实现一个简单的同步 RAM

reg [7:0] mem [0:255]; // 256×8 的存储器

always @(posedge clk) begin

if (we)

mem[addr] <= din;

dout <= mem[addr];

end综合工具会自动将上述代码推断为 Block RAM,而非用 LUT 实现。

💡 工程师手记:刚开始学 FPGA 时,我犯过一个错误:用

reg [7:0] big_array [0:65535]声明了一个 64K 的数组,结果综合时 LUT 用了 90% 以上,时序全崩了。后来才知道,大容量存储必须用 Block RAM,而不是让综合工具用 LUT 来”硬堆”。写代码时遵循特定的编码风格(比如同步读写),综合工具才能正确推断为 BRAM。

6. 全局网络:时钟与控制信号的高速通道

在 FPGA 设计中,有些信号的扇出(Fanout)极大——需要同时驱动成千上万个触发器。这类信号需要走全局网络,而非普通布线。

典型的高扇出信号:

| 信号类型 | 特点 |

|---|---|

| 时钟信号 | 驱动整个设计中的所有寄存器,扇出最大 |

| 复位信号 | 将所有寄存器初始化,扇出仅次于时钟 |

| 使能/清零信号 | 控制特定模块的运行状态 |

FPGA 内部有专用的全局时钟网络(Global Clock Network),通过 PLL/MMCM 对时钟进行管理后,通过低偏斜(Low Skew)的专用布线分发到整个芯片。

⚠️ 设计建议:不要在设计中滥用复位信号。大量使用异步复位会消耗全局布线资源,增加布局布线难度。现代 FPGA 设计推荐使用同步复位,并且只对确实需要复位的寄存器添加复位逻辑。

7. 总结

| 资源 | 核心作用 | 你需要知道的一件事 |

|---|---|---|

| CLB(LUT + FF) | 实现所有逻辑 | LUT 是查表,不是计算——6输入任意函数,延迟恒定 |

| IOB | 芯片与外界的接口 | 同一 Bank 必须用相同电压标准,引脚分配要提前规划 |

| 可编程互联 | 连接一切资源 | 资源利用率控制在 70-80%,否则布线拥堵影响时序 |

| Block RAM | 片上高速存储 | 大容量存储用 BRAM,别用 LUT 硬堆 |

| DSP Slice | 乘加运算加速 | 写 a * b 综合工具会自动用 DSP |

| PLL/MMCM | 时钟管理 | 不要直接用外部时钟,先过 PLL |

| 全局网络 | 时钟/复位分发 | 少用异步复位,推荐同步复位 |

这篇文章覆盖了 FPGA 内部资源的全局认知。每种资源的深入细节(如 SRL 的高级用法、IOB 的时序约束、DSP 的级联模式等),我们会在后续的进阶文章中展开。

常见问题

Q1:综合报告里的 LUT 利用率多少算正常?

一般控制在 70% 以下比较安全。超过 80% 布线会变得困难,时序容易不收敛。如果利用率过高,考虑升级芯片或优化设计。

Q2:Block RAM 和分布式 RAM(LUT RAM)怎么选?

小容量(<64 bit)且需要极低延迟 → 分布式 RAM(SliceM 的 LUT)。大容量(>1Kb)→ Block RAM。综合工具通常会自动选择,但你可以用属性

(* ram_style = "block" *)或(* ram_style = "distributed" *)强制指定。

Q3:为什么我的加法器时序不过关?

可能是位宽太宽导致进位链太长。解决方案:① 流水线拆分(把 32 位加法拆成两级 16 位)② 降低时钟频率 ③ 检查是否正确使用了 Carry Chain(而非被综合成 LUT 级联)。

Q4:什么时候需要手动例化硬核 IP?

大多数情况下不需要——综合工具会自动推断 Block RAM、DSP、进位链等。但以下场景可能需要手动例化:① 使用 PLL/MMCM 生成时钟 ② 使用 SerDes 高速收发器 ③ 使用 PCIe 硬核 ④ 需要精确控制 BRAM 配置模式。

参考资料

- Xilinx/AMD,UG474: 7 Series FPGAs Configurable Logic Block User Guide

- Xilinx/AMD,UG471: 7 Series FPGAs SelectIO Resources User Guide

- Xilinx/AMD,UG473: 7 Series FPGAs Memory Resources User Guide

- Xilinx/AMD,UG479: 7 Series FPGAs DSP48E1 Slice User Guide

系列导航:本文是「FPGA 入门系列」第 4 篇。

- 上一篇:FPGA 芯片怎么选?主流厂商与产品线全景指南

- 下一篇:FPGA 开发流程全解析

如果这篇文章对你有帮助,欢迎点赞、收藏,也欢迎在评论区分享你对 FPGA 内部资源的理解或疑问。